P2020NXE2KFC Microprocessors MPU P2020E ET 1000/667 R2.1

♠ Product Description

| Product Attribute | Attribute Value |

| Manufacturer: | NXP |

| Product Category: | Microprocessors - MPU |

| Shipping Restrictions: | This product may require additional documentation to export from the United States. |

| RoHS: | Details |

| Mounting Style: | SMD/SMT |

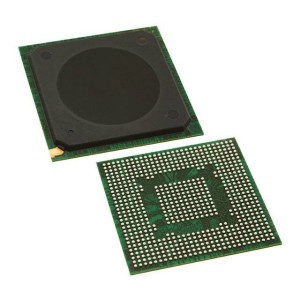

| Package / Case: | PBGA-689 |

| Series: | P2020 |

| Core: | e500-v2 |

| Number of Cores: | 2 Core |

| Data Bus Width: | 32 bit |

| Maximum Clock Frequency: | 1 GHz |

| L1 Cache Instruction Memory: | 32 kB |

| L1 Cache Data Memory: | 32 kB |

| Operating Supply Voltage: | 1.05 V |

| Minimum Operating Temperature: | - 40 C |

| Maximum Operating Temperature: | + 125 C |

| Packaging: | Tray |

| Brand: | NXP Semiconductors |

| I/O Voltage: | 1.5 V, 1.8 V, 2.5 V, 3.3 V |

| Instruction Type: | Floating Point |

| Interface Type: | Ethernet, I2C, PCIe, SPI, UART, USB |

| L2 Cache Instruction / Data Memory: | 512 kB |

| Memory Type: | L1/L2 Cache |

| Moisture Sensitive: | Yes |

| Number of I/Os: | 16 I/O |

| Processor Series: | QorIQ |

| Product Type: | Microprocessors - MPU |

| Factory Pack Quantity: | 27 |

| Subcategory: | Microprocessors - MPU |

| Tradename: | QorIQ |

| Watchdog Timers: | No Watchdog Timer |

| Part # Aliases: | 935319659557 |

| Unit Weight: | 0.185090 oz |

The following list provides an overview of the P2020 feature set:

• Dual high-performance Power Architecture® e500 cores.

• 36-bit physical addressing

– Double-precision floating-point support

– 32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache for each core

– 800-MHz to 1.33-GHz clock frequency

• 512 Kbyte L2 cache with ECC. Also configurable as SRAM and stashing memory.

• Three 10/100/1000 Mbps enhanced three-speed Ethernet controllers (eTSECs)

– TCP/IP acceleration, quality of service, and

classification capabilities

– IEEE Std 1588™ support

– Lossless flow control

– R/G/MII, R/TBI, SGMII

• High-speed interfaces supporting various multiplexing options:

– Four SerDes to 3.125 GHz multiplexed across controllers

– Three PCI Express interfaces

– Two Serial RapidIO interfaces

– Two SGMII interfaces

• High-Speed USB controller (USB 2.0)

– Host and device support

– Enhanced host controller interface (EHCI)

– ULPI interface to PHY

• Enhanced secure digital host controller (SD/MMC) Enhanced Serial peripheral interface (eSPI)

• Integrated security engine

– Protocol support includes SNOW, ARC4, 3DES, AES, RSA/ECC, RNG, single-pass SSL/TLS, Kasumi

– XOR acceleration

• 64-bit DDR2/DDR3 SDRAM memory controller with ECC support

• Programmable interrupt controller (PIC) compliant with OpenPIC standard

• Two four-channel DMA controllers

• Two I2C controllers, DUART, timers

• Enhanced local bus controller (eLBC)

• 16 general-purpose I/O signals

• Operating junction temperature

• 31 × 31 mm 689-pin WB-TePBGA II (wire bond temperature-enhanced plastic BGA)