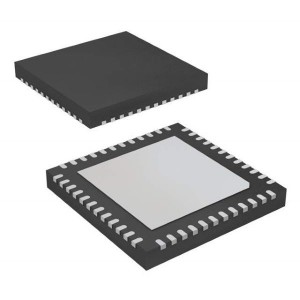

SPC563M64L5COAR 32-bit Microcontrollers – MCU 32-BIT Embedded MCU 80 MHz, 1.5 Mbyte

♠ Product Description

| Product Attribute | Attribute Value |

| Manufacturer: | STMicroelectronics |

| Product Category: | 32-bit Microcontrollers - MCU |

| RoHS: | Details |

| Series: | SPC563M64L5 |

| Mounting Style: | SMD/SMT |

| Package/Case: | LQFP-144 |

| Core: | e200z335 |

| Program Memory Size: | 1.5 MB |

| Data RAM Size: | 94 kB |

| Data Bus Width: | 32 bit |

| ADC Resolution: | 2 x 8 bit/10 bit/12 bit |

| Maximum Clock Frequency: | 80 MHz |

| Number of I/Os: | 105 I/O |

| Supply Voltage - Min: | 5 V |

| Supply Voltage - Max: | 5 V |

| Minimum Operating Temperature: | - 40 C |

| Maximum Operating Temperature: | + 125 C |

| Qualification: | AEC-Q100 |

| Packaging: | Reel |

| Packaging: | Cut Tape |

| Packaging: | MouseReel |

| Brand: | STMicroelectronics |

| Moisture Sensitive: | Yes |

| Product Type: | 32-bit Microcontrollers - MCU |

| Factory Pack Quantity: | 500 |

| Subcategory: | Microcontrollers - MCU |

| Unit Weight: | 1.290 g |

♠ 32-bit Power Architecture® based MCU for automotive powertrain applications

These 32-bit automotive microcontrollers are a family of System-on-Chip (SoC) devices that contain many new features coupled with high performance 90 nm CMOS technology to provide substantial reduction of cost per feature and significant performance improvement. The advanced and cost-efficient host processor core of this automotive controller family is built on Power Architecture® technology. This family contains enhancements that improve the architecture’s fit in embedded applications, includes additional instruction support for Digital Signal Processing (DSP), integrates technologies—such as an enhanced time processor unit, enhanced queued analog-to-digital converter, Controller Area Network, and an enhanced modular input-output system—that are important for today’s lower-end powertrain applications. The device has a single level of memory hierarchy consisting of up to 94 KB on-chip SRAM and up to 1.5 MB of internal flash memory. The device also has an External Bus Interface (EBI) for ‘calibration’.

■ Single issue, 32-bit Power Architecture® Book E compliant e200z335 CPU core complex

– Includes Variable Length Encoding (VLE) enhancements for code size reduction

■ 32-channel Direct Memory Access controller (DMA)

■ Interrupt Controller (INTC) capable of handling 364 selectable-priority interrupt sources: 191 peripheral interrupt sources, 8 software interrupts and 165 reserved interrupts.

■ Frequency-Modulated Phase-Locked Loop (FMPLL)

■ Calibration External Bus Interface (EBI)(a)

■ System Integration Unit (SIU)

■ Up to 1.5 Mbyte on-chip Flash with Flash controller

– Fetch Accelerator for single cycle Flash access @80 MHz

■ Up to 94 Kbyte on-chip static RAM (including up to 32 Kbyte standby RAM)

■ Boot Assist Module (BAM)

■ 32-channel second-generation enhanced Time Processor Unit (eTPU)

– 32 standard eTPU channels

– Architectural enhancements to improve code efficiency and added flexibility

■ 16-channels enhanced Modular Input-Output System (eMIOS)

■ Enhanced Queued Analog-to-Digital Converter (eQADC)

■ Decimation filter (part of eQADC)

■ Silicon die temperature sensor

■ 2 Deserial Serial Peripheral Interface (DSPI) modules (compatible with Microsecond Bus)

■ 2 enhanced Serial Communication Interface (eSCI) modules compatible with LIN

■ 2 Controller Area Network (FlexCAN) modules that support CAN 2.0B

■ Nexus Port Controller (NPC) per IEEE-ISTO 5001-2003 standard

■ IEEE 1149.1 (JTAG) support

■ Nexus interface

■ On-chip voltage regulator controller that provides 1.2 V and 3.3 V internal supplies from a 5 V external source.

■ Designed for LQFP144, and LQFP176